# Polyfluorene-Sorted, Carbon Nanotube Array Field-Effect Transistors with Increased Current Density and High On/Off Ratio

Gerald J. Brady,<sup>†</sup> Yongho Joo,<sup>†</sup> Meng-Yin Wu,<sup>‡</sup> Matthew J. Shea,<sup>†</sup> Padma Gopalan,<sup>†</sup> and Michael S. Arnold<sup>\*,†</sup>

<sup>†</sup>Department of Materials Science and Engineering and <sup>‡</sup>Department of Electrical and Computer Engineering, University of Wisconsin—Madison, Madison, Wisconsin 53706, United States

**ABSTRACT** Challenges in eliminating metallic from semiconducting single-walled carbon nanotubes (SWCNTs) and in controlling their alignment have limited the development of high-performance SWCNT-based field-effect transistors (FETs). We recently pioneered an approach for depositing aligned arrays of ultra-high-purity semiconducting SWCNTs, isolated using polyfluorene derivatives, called dose-controlled floating evaporative self-assembly. Here, we tailor FETs fabricated from these arrays to achieve on-conductance ( $G_{on}$ ) per width and an on-off ratio ( $G_{on}/G_{off}$ ) of 261  $\mu$ S/ $\mu$ m and 2  $\times$  10<sup>5</sup>, respectively, for a channel length ( $L_{ch}$ ) of 240 nm and 116  $\mu$ S/ $\mu$ m and 1  $\times$  10<sup>6</sup>,

respectively, for an  $L_{ch}$  of 1  $\mu$ m. We demonstrate 1400× greater  $G_{on}/G_{off}$  than SWCNT FETs fabricated by other methods, at comparable  $G_{on}$  per width of  $\sim 250 \,\mu$ S/ $\mu$ m and 30 $-100\times$  greater  $G_{on}$  per width at comparable  $G_{on}/G_{off}$  of 10<sup>5</sup> $-10^7$ . The average  $G_{on}$  per tube reaches 5.7  $\pm$  1.4  $\mu$ S at a packing density of 35 tubes/ $\mu$ m for  $L_{ch}$  in the range 160–240 nm, limited by contact resistance. These gains highlight the promise of using ultra-high-purity semiconducting SWCNTs with controlled alignment for next-generation semiconductor electronics.

KEYWORDS: field-effect transistor · semiconducting · alignment · conductance · contact resistance · mobility

ingle-walled carbon nanotubes (SWCNTs) have been widely recognized as promisling candidates for next-generation field-effect transistors (FETs). The electronic properties of individual SWCNTs have been studied extensively in the diffuse (>1000 nm) and ballistic (<100 nm) charge transport regimes, revealing exceptional field-effect mobility<sup>1</sup> as high as 80 000 cm<sup>2</sup>/V/s and ballistic quantum conductance,<sup>2</sup> respectively. In FETs with a channel length  $(L_{ch})$ shorter than 10 nm, like those planned for future integrated circuits, semiconducting SWCNTs are expected to outperform silicon, allowing for  $2 \times$  the current density<sup>3,4</sup> with  $2-3 \times$  lower power consumption.<sup>5,6</sup> In order to realize these gains in next-generation integrated circuits, it will be necessary to build FETs not from individual SWCNTs but aligned and tightly packed arrays of them.<sup>7</sup> However, thus far, it has been difficult to fully exploit the exceptional properties of individual SWCNTs in arrays because of materials challenges in the alignment and placement

of SWCNTs, as well as in the removal of metallic SWCNTs.

The approaches that have been developed to create aligned SWCNT array FETs can be divided into two categories: (1) the direct growth of aligned SWCNTs via chemical vapor deposition and (2) their postsynthetic sorting and assembly. Progress has been made in improving directly grown SWCNT arrays by selectively heating<sup>8</sup> and burning<sup>9–11</sup> and thereby removing metallic SWCNTs and also in increasing the SWCNT density via iterative growth and transfer approaches.<sup>12–14</sup> Likewise, a number of postsynthetic sorting methods have been developed to separate metallic and semiconducting SWCNTs<sup>15–19</sup> and then to align them in arrays.<sup>20-27</sup> These advances have made it possible to increase the conductance  $(G_{op})$ per width and conductance modulation  $(G_{on}/G_{off})$  of both types of SWCNT FETs.<sup>28–33</sup> Nonetheless, current state-of-the-art array FETs still substantially underperform what should be realistically possible. It has especially been

\* Address correspondence to msarnold@wisc.edu.

Received for review August 29, 2014 and accepted November 10, 2014.

Published online November 10, 2014 10.1021/nn5048734

© 2014 American Chemical Society

VOL.8 • NO.11 • 11614-11621 • 2014

11614

difficult to simultaneously achieve high Gon per width and  $G_{\rm on}/G_{\rm off}$  in the same FET. This difficulty likely arises from residual metallic SWCNTs and organizational disorder, which can decrease both  $G_{\rm on}$  and  $G_{\rm on}/G_{\rm off}$ .

Recently, we discovered a promising route toward overcoming these challenges. We pioneered an approach for depositing aligned arrays of highly purified semiconducting SWCNTs, isolated using polyfluorene derivatives, called dose-controlled, floating evaporative self-assembly (FESA).<sup>34</sup> In the initial screening of FETs fabricated from these arrays, we reported  $G_{on}$  per width of 61  $\mu$ S/ $\mu$ m with a  $G_{on}/G_{off}$  of  $\sim 10^5$  for FETs with  $L_{ch}$  = 400 nm and a packing density of 45 tubes/ $\mu$ m.<sup>35</sup> Here, we tailor FETs fabricated from these arrays to increase Gon per width by more aggressively scaling L<sub>ch</sub>, improving the gate-coupling efficiency and improving the contact resistance and SWCNT processing parameters. Next, we more extensively evaluate the performance parameters of the SWCNT arrays using a Y function method to estimate the intrinsic channel conductance of the SWCNT FETs as a function of  $L_{ch}$ . Finally, we implement realistic models for the channelgate capacitance that include disorder in the arrays to determine charge transport mobility in the percolating, long-channel regime (when  $L_{ch}$  is greater than the average SWCNT length and the aligned SWCNTs must percolate to span the channel) and to estimate a lower bound for the mobility in the direct, short-channel regime (when L<sub>ch</sub> is less than the average SWCNT length and most of the SWCNTs directly span the channel).

### **RESULTS AND DISCUSSION**

To fabricate FETs, we start with heterogeneous SWCNT soot grown by the arc discharge method. Ultra-high-purity semiconducting SWCNTs with diameters between 1.3 and 1.8 nm are extracted using the selective polymer poly[(9,9-dioctylfluorenyl-2,7diyl)-alt-co-(6,6'-[2,2'-bipyridine])] (PFO-BPy) in toluene, adapting the procedures of Mistry et al. and our previous work.<sup>36,37</sup> The individual SWCNTs have a log-normal length distribution with an average length of 580 nm (Figure S1a,b). The purity and quality of the SWCNT material are verified via absorbance before alignment and FET fabrication in Figure S2a.

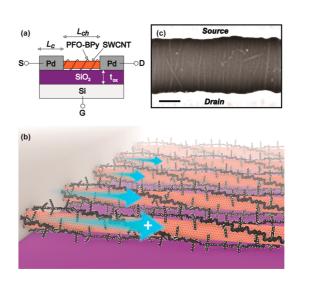

The SWCNTs are deposited as aligned arrays on HMDS/SiO<sub>2</sub>/Si substrates via dose-controlled FESA at a packing density ( $\rho$ ) of 28–49 tubes/ $\mu$ m.<sup>34</sup> Schematics of the FET architecture are shown in Figures 1a,b. Pd source and drain electrodes with a contact length  $(L_c)$ of 1.2  $\mu$ m, a SiO<sub>2</sub> back-gate dielectric, and a heavily doped Si back-gate electrode are used. The channel width ( $W_{ch}$ ) is 3.8  $\mu$ m (about 104–185 SWCNTs), and  $L_{ch}$  is varied from 160 to 3070 nm. Experimental methods are further detailed below. Electron and atomic force micrographs (Figures 1c and S3) show that the SWCNTs are well aligned, with their long axis extending from source to drain.

Figure 1. (a) Schematic of SWCNT FET architecture (not to scale). (b) Schematic of PFO-BPy-wrapped SWCNT arrays. (c) Top-down scanning electron micrograph of SWCNTs spanning Pd electrodes of a 240 nm Lch SWCNT FET (scale bar = 100 nm).

In the initial screening of FETs fabricated from these arrays,  $G_{on}$  per width was limited to about 60  $\mu$ S/ $\mu$ m for  $L_{ch} = 400 \text{ nm.}^{35}$  Here, we make several changes to increase Gon per tube and thus Gon per width. Namely, (1) we optimize the procedures by which excess polymer residues are removed from the aligned SWCNT arrays. In our initial work, we used short ultraviolet ozone radiation to reduce polymer residues. However, here we show that this treatment is detrimental, decreasing  $G_{on}$  per tube (Figure S4a). We instead use more extensive solvent rinsing and thermal annealing to reduce polymer residues (Figure S4b). (2) We decrease the total sonication time of the SWCNT solution from 31 min to 6 min (Figure S2b). (3) We decrease the SiO<sub>2</sub> gate oxide thickness from 90 nm to 15 nm to improve the capacitive coupling to the SWCNT array (Figure S5). We summarize the results in Figure S6 and demonstrate a 6-fold improvement in  $G_{\rm on}$  per tube compared to the initial screening.

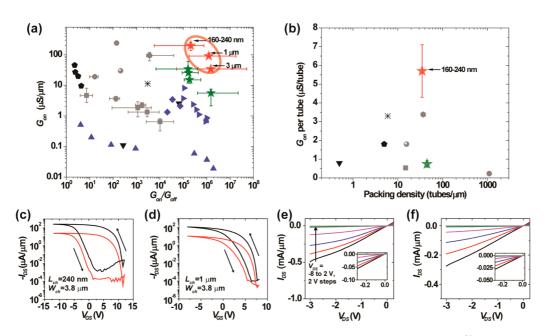

We examine three metrics to compare the properties of the optimized devices with the current state of the art:  $G_{on}$  per width,  $G_{on}/G_{off}$ , and  $G_{on}$  per tube as a function of packing density. The mean and standard deviation of  $G_{on}$  per width and  $G_{on}/G_{off}$  of the optimized FETs for  $L_{ch} = 160-240$  nm, 1  $\mu$ m, and 3  $\mu$ m are compared to the current state of the art in Figure 2a.<sup>8,11,24,38–45</sup>  $G_{on}$  per width of the optimized FETs is increased by a factor of 6, on average, at constant Gon/Goff, compared to our initial screening (Table 1). The device-to-device variability in Gon per width of 20% for direct transport devices is typical for SWCNT array FETs.<sup>46</sup> When counting the exact number of SWCNTs that span the channel in each device, the variability in  $G_{\rm on}$  per tube is a similar  ${\sim}25\%$  (see below).<sup>33</sup> Thus, other factors must be contributing to the variability in Gon. Overall, these FETs demonstrate

VOL.8 • NO.11 • 11614-11621 • 2014

A

Figure 2. (a)  $G_{on}$  per width versus  $G_{on}/G_{off}$  literature comparison: Aligned CVD (black): pentagon,<sup>39</sup> down-triangles,<sup>8</sup> asterisk.<sup>11</sup> Postsynthetic random (blue): up-triangles,<sup>44</sup> left-triangle,<sup>42</sup> right-triangles,<sup>43</sup> diamonds.<sup>40</sup> Postsynthetic aligned (gray): squares,<sup>38</sup> circles,<sup>24</sup> hexagon,<sup>45</sup> sphere.<sup>41</sup> This work: optimized SWCNTs (red stars), initial screening (green stars).<sup>35</sup> (b)  $G_{on}$  per tube versus packing density for aligned SWCNT FETs presented in (a). (c) Transfer characteristics at  $V_{DS} = -1$  V (black) and -0.1 V (red) for a champion SWCNT FET ( $L_{ch} = 240$  nm and  $W_{ch} = 3.8 \,\mu$ m). (d) Transfer characteristics of the device in (c) with  $V_{GS}$  swept from -8 V (black) to 2 V (gray) in 2 V increments. (f) Output characteristics of the device in (d).

TABLE 1. Comparison of Optimized SWCNT FET-Extracted Parameters at Various L<sub>ch</sub>

| L <sub>ch</sub> (nm)                     | G <sub>on</sub> per width (μS/μm) | log(G <sub>on</sub> /G <sub>off</sub> ) | $G_{ m on}$ per tube ( $\mu$ S/tube) | $\mu$ (cm²/V/s) |

|------------------------------------------|-----------------------------------|-----------------------------------------|--------------------------------------|-----------------|

| 160—240                                  | 197 $\pm$ 38                      | $5.13\pm0.67$                           | $5.7\pm1.4$                          |                 |

| 1070                                     | $95\pm10$                         | $6.1\pm0.74$                            | $2.4\pm0.3$                          | $183\pm18$      |

| 3070                                     | $34\pm3$                          | $6.2\pm1.22$                            | $0.94\pm0.15$                        | $179\pm10$      |

| initial screening <sup>35</sup> (400 nm) | $37\pm9$                          | $4.9\pm0.7$                             | $0.74\pm0.16$                        |                 |

1400× greater  $G_{\rm on}/G_{\rm off}$  than SWCNT FETs made via other methods, at comparable  $G_{\rm on}$  per width of ~250  $\mu$ S/ $\mu$ m,<sup>24</sup> and 30–100× greater  $G_{\rm on}$  per width, at comparable  $G_{\rm on}/G_{\rm off}^{43}$  of 10<sup>5</sup>–10<sup>7</sup> (Figure 2a).

The average  $G_{on}$  per tube for devices with  $L_{ch} = 160-240$  nm is  $5.7 \pm 1.4 \,\mu$ S/tube at a packing density of  $35 \pm 6$  tubes/ $\mu$ m. For comparison in Figure 2b, in previous array FETs,  $G_{on}$  per tube has been limited to less than  $3.4 \,\mu$ S/tube. The  $G_{on}$  per tube reported here does not seem to be affected by internanotube screening effects because the  $G_{on}$  per tube in the aligned SWCNT FETs is equivalent to that measured in isolated SWCNT FETs fabricated from dilute spin-cast films. The product of the high  $G_{on}$  per tube and high packing density achieved here enables the high  $G_{on}$  per width.

The current–voltage characteristics of champion devices are shown in Figure 2c–f for FETs with  $L_{ch}$  of 240 and 1070 nm. Hysteresis is present, which is expected for back-gated SWCNT FETs measured in ambient.<sup>8,47,48</sup> The magnitude of the hysteresis may be affected by solvent or polymer wrapper residues and will be the focus of future studies. At an  $L_{ch}$  of

BRADY ET AL.

240 nm,  $G_{\rm on}$  per width and  $G_{\rm on}/G_{\rm off}$  are 261  $\mu$ S/ $\mu$ m and 2 × 10<sup>5</sup>, respectively. The current output is 7.2  $\mu$ A/tube at  $V_{\rm DS} = -1.0$  V. At an  $L_{\rm ch}$  of 1070 nm,  $G_{\rm on}$  per width and  $G_{\rm on}/G_{\rm off}$  are 120  $\mu$ S/ $\mu$ m and 1 × 10<sup>6</sup>, respectively. Although  $L_{\rm ch}$  is about 4 times longer in the latter FET compared with the former, the conductance only decreases 2-fold, suggesting that contact resistance (2 $R_c$ ) somewhat limits transport in the short  $L_{\rm ch}$  regime.

Next, we analyze each device using a Y function method (YFM) to quantify  $2R_c$ .<sup>49</sup> Contact resistance at the electrode–SWCNT interface may arise from residues on the SWCNT surfaces following deposition that are not fully removed *via* postdeposition processing. These residues may originate from the polymer wrappers used to sort and disperse the SWCNTs or from solvents or polymers used during device fabrication. Short SWCNT–metal contact length may also lead to contact resistance.<sup>50</sup> Even though the length of our contacts is 1.2  $\mu$ m, the latter is important because the average SWCNT length is only 580 nm. YFM is commonly used to extract device parameters for Si MOSFETs and was recently adapted for SWCNT FETs to

VOL. 8 • NO. 11 • 11614-11621 • 2014

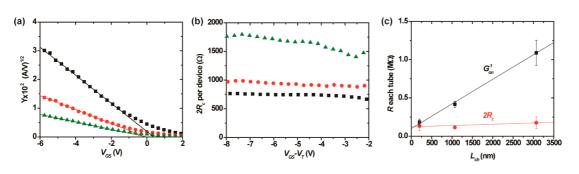

Figure 3. (a) YFM fits for representative FETs with L<sub>ch</sub> = 200 nm (black squares), 1070 nm (red circles), and 3070 nm (green triangles). (b)  $2R_c$  fit for the same devices in (a). (c) Measured  $G_{on}^{-1}$  (black squares) and  $2R_c$  calculated by YFM (red circles) for the FETs presented in Figure 2a at various channel lengths (160-240 nm = 11 devices, 1070 nm = 4 devices, 3070 nm = 3 devices). Error bars denote one standard deviation.

measure  $2R_c$ .<sup>51,52</sup> To perform YFM analysis, the output current and transconductance are measured in the linear regime of the  $I_{DS}-V_{GS}$  transfer curve at gate biases ranging from 1.2 to 8.0 V less than the threshold voltage  $(V_{\rm T})$ . The Y function is plotted for three representative devices in Figure 3a with L<sub>ch</sub> of 200, 1070, and 3070 nm following the relationship

$$Y = \frac{I_{\rm DS}}{g_{\rm m}^{1/2}} = (g_{\rm ch} V_{\rm DS})^{1/2} (V_{\rm GS} - V_{\rm T})$$

(1)

where  $g_{ch} = \mu(W/L)C_{ox}$  is the  $2R_c$ -independent transconductance and is extracted from the slope of the linear region of the Y versus  $V_{GS}$  plot (Figure 3a).<sup>49</sup> The  $q_{ch}$  is further used below to calculate channel mobility based on YFM calculation. The threshold voltage  $(V_T)$  is determined from the x-axis intercept and is further used to calculate  $2R_c$  according to

$$2R_{\rm c} = \frac{V_{\rm DS}}{I_{\rm DS}} - \frac{V_{\rm DS}}{g_{\rm ch}(V_{\rm GS} - V_{\rm T})}$$

(2)

The extracted  $2R_c$  of the three devices characterized in Figure 3a is analyzed as a function of  $V_{GS}$  in Figure 3b, demonstrating minimal  $V_{GS}$  dependence.  $2R_c$  is averaged over a range of  $V_{GS}$  in the linear regime of Figure 3a. The mean and standard deviation of  $2R_c$ on a single tube basis for all 18 devices are 136 and 60 k $\Omega$ , respectively. The minimum and maximum  $2R_c$ are 66 and 260 k $\Omega$ , respectively. The large variability in  $2R_c$  is separately confirmed using an  $L_{ch}$ -dependent transmission line method (TLM) to analyze the contact resistance of neighboring devices. The  $2R_c$  determined *via* TLM similarly varies from 64 to 225 k $\Omega$  on a single tube basis (Figure S7a,b). The variation in  $2R_c$  can potentially be attributed to residues or adsorbates that are not uniform on the substrate or to irregularities in the SWCNT packing arrangement that vary from device to device. The 2R<sub>c</sub> variability is largely responsible for the device-to-device variability in Gon mentioned previously for  $L_{ch} = 160-240$  nm.

We next compare  $2R_c$  to the on-state device resistance  $(G_{on}^{-1})$  on a single tube basis in Figure 3c.  $G_{on}^{-1}$ increases with increasing  $L_{ch}$ , while  $2R_c$  remains fairly constant. At L<sub>ch</sub> of 3070 nm, the SWCNTs percolate to span the FET channel, and  $G_{\rm on}^{-1}$  and  $2R_{\rm c}$  are 1.1  $\pm$ 0.17 M\Omega and 176  $\pm$  78 kΩ, respectively, where the error bars denote device-to-device variability. The contact resistance contributes 8-21% of the total device resistance. At an L<sub>ch</sub> of 160–240 nm, most of the SWCNTs directly span the channel, and  $G_{on}^{-1}$  and  $2R_{\rm c}$  are 185  $\pm$  39 k $\Omega$  and 132  $\pm$  57 k $\Omega$ , respectively, which are comparable to each other. In this direct transport regime, the devices are  $2R_c$  limited and the contact resistance may roughly contribute anywhere from 50% to nearly 100% of the total on-state device resistance. The value of  $2R_c$  is larger than the  $\sim 10 \text{ k}\Omega$ that should ultimately be possible according to single SWCNT measurements.<sup>50</sup> However, the  $2R_c$  of our champion devices ( $\sim$ 70 k $\Omega$ ) is comparable to the lowest  $2R_c$  that has been reported in CVD-grown aligned array FETs.<sup>53,54</sup> The  $2R_c$  of solution-processed aligned array FETs has typically been much larger; for example, Cao et al. report a  $2R_c$  of  $6 M\Omega$ .<sup>24</sup> The relatively low  $2R_c$  is one reason that we achieve a high  $G_{on}$  per tube.

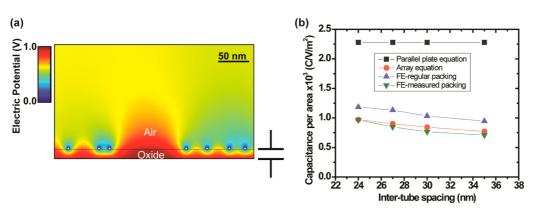

Next, the charge transport mobility,  $\mu$ , is quantified in the percolating, long-channel regime, and a lower bound for  $\mu$  is estimated in the direct, short-channel regime. The gate – channel capacitance per area ( $C_{arrav}$ ) is evaluated in two ways. In the first approach, a regular array approximation is used where

$$C_{\text{array}} = \frac{\rho}{\left[C_{\text{Q}}^{-1} + \frac{1}{2\pi\varepsilon_{0}\varepsilon_{\text{r}}}\ln\left(\frac{\sinh(2\pi t_{\text{ox}}\rho)}{\pi r\rho}\right)\right]}$$

(3)

and  $C_{\rm O} = 4 \times 10^{-10}$  F/m is the quantum capacitance,  $\varepsilon_0$ is the relative permittivity of free space,  $\varepsilon_r = (3.9 + 1)/2$ is the dielectric constant of the SiO<sub>2</sub>/air interface,  $t_{ox} =$ 15 nm is the oxide thickness, r = 0.7 nm is the average radius of the SWCNT, and  $\rho$  is the linear SWCNT packing density. The array equation approach is valid assuming that the inter-SWCNT spacing exceeds the dielectric thickness,<sup>39</sup> which is true on average for the devices presented here. However, this approximation may not properly account for irregularities and disorder in the packing arrangement.

In the second approach, we calculate Carray via finite element (FE) modeling using COMSOL (COMSOL, Inc.,

Figure 4. (a) Modeled electrostatic potential map of a measured SWCNT FET cross-section in COMSOL. The thickness of the oxide is 15 nm, with an average intertube spacing of 35 nm. The figure shows a 500 nm selected region of the 3.8  $\mu$ m wide FET. (b) Summary of the gate-channel capacitance calculated for parallel plate equation (black squares), array equation (red circles), FE-regular packing (blue up-triangles), and FE-measured packing (green down-triangles).

Burlington, MA, USA) and considering disorder in SWCNT–SWCNT spacing. Disorder is quantified by measuring the position of each SWCNT in each FET *via* electron microscopy, across a cross-section extending along the center of the entire width of each channel (Figures 4a and S8).  $C_Q$  is then added in series with the capacitance calculated from the FE modeling according to

$$C_{\text{array}} = [C_Q^{-1} + C_{\text{FE}}^{-1}]^{-1}$$

(4)

A summary of the calculated gate—channel capacitances for various models and intertube spacing is presented in Figure 4b. The calculated capacitance for the measured packing arrangement is about 6% smaller than that determined from the array equation approximation and is used to determine the mobility at  $V_{\rm DS} = -0.1$  V according to

$$\mu = \frac{L_{\rm ch}g_{\rm ch}}{C_{\rm array}W_{\rm ch}} \tag{5}$$

At  $L_{ch} = 3070$  nm in the percolating, long-channel regime, in which Gon is dominated by intra-SWCNT and SWCNT–SWCNT resistance,  $\mu$  is 179  $\pm$  10 cm<sup>2</sup>/V/s, where the mean and standard deviation are calculated for the three devices measured.  $\mu$  is similar at  $L_{ch} = 1070$  nm. At  $L_{ch} = 160-240$  nm in the direct, shortchannel regime, charge transport is still expected to be diffusive. Studies of transport by Cao et al. of solutionprocessed SWCNTs have shown that transport is diffusive even at L<sub>ch</sub> as small as 150 nm.<sup>52</sup> The YFM analysis of  $\mu$  in the short-channel regime is less accurate because the contact resistance constitutes at least 50% of the onstate resistance. Therefore, to minimize the uncertainty, we analyze only a subset of devices with the smallest  $2R_{\rm c}$ . The calculated  $\mu$  ranges from 320 to 410 cm<sup>2</sup>/V/s (Figure S9). The  $\mu$  determined in both the short- and long-channel regimes via TLM analysis is similar (Figure S9). The increase in  $\mu$  for  $L_{ch}$  < 300 nm likely arises because most of the SWCNTs directly span the channel, eliminating SWCNT-SWCNT resistance.

It should be noted that the  $\mu$  determined in the direct regime is likely a lower bound for the actual  $\mu$  because YFM and TLM analyses underestimate  $\mu$  when  $2R_c$  varies from SWCNT to SWCNT within one FET and  $2R_c$  and  $G_{on}^{-1}$  are similar. The large variation of  $2R_c$  from FET to FET suggests that  $2R_c$  may vary within a single FET, as well. More extensive characterization of transport in the direct regime will be the focus of future study.

Regardless of whether  $\mu$  is 320 to 410 cm<sup>2</sup>/V/s or larger, the on-conductance of aggressively scaled sub-50 nm channels will almost certainly be limited by contact resistance, even if the contact resistance is substantially reduced. Thus, in order to increase on-conductance, future research should focus less on increasing mobility and more on decreasing contact resistance. Compared to CVD SWCNTs, the benefit of solution-processed SWCNTs is that it may be possible to achieve higher packing densities by circumventing the burn-out processes needed to eliminate metallic SWCNTs in CVD arrays. Thus, if contact resistance is optimized, the  $G_{on}$  per width should ultimately be higher for solution-processed SWCNTs, with the potential to outperform Si MOSFETs.

The fact that the mobility is still high, 180 cm<sup>2</sup>/V/s, at long channel lengths indicates that the SWCNT– SWCNT coupling is excellent in the FESA-deposited SWCNT arrays, making them promising for more coarsely patterned FETs with >1  $\mu$ m long channels. The alignment of the SWCNTs likely leads to substantially larger tube–tube overlap in comparison to the typical cross-junction overlap observed in percolating random networks. The mobility in the long-channel regime exceeds the ~100 cm<sup>2</sup>/V/s that can be achieved using state-of-the-art inorganic amorphous semiconductors such as indium gallium zinc oxide.<sup>55</sup>

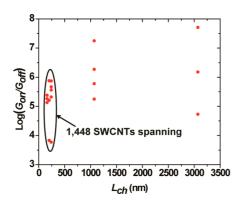

A final consideration is the semiconducting purity of the SWCNTs, which is evaluated by measuring  $G_{on}/G_{off}$  of the direct transport FETs and counting the number of tubes spanning each FET *via* SEM images. All of the SWCNT FETs measured have a  $G_{on}/G_{off}$  of >5  $\times$  10<sup>3</sup> with

agnanc www.acsnano.org

Figure 5. Log of on–off ratio for 18 devices with 11 devices measured at  $L_{\rm ch}$  < 240 nm, four devices measured at  $L_{\rm ch}$  = 1070 nm, and three devices measured at  $L_{\rm ch}$  = 3070 nm.  $W_{\rm ch}$  of all devices is 3.8  $\mu$ m with similar packing density of about 40 tubes/ $\mu$ m.

most FETs having a  $G_{on}/G_{off}$  of  $\geq 10^5$  (Figure 5), where a  $G_{on}/G_{off}$  of less than  $10^2$  indicates the presence of a metallic SWCNT. These data include more than 1448 SWCNTs measured in FETs with an  $L_{ch}$  of  $\leq 240$  nm, which directly span the channel, indicating that the metallic SWCNT impurity concentration is below one part per 1448. When our previous work is taken into consideration (4071 semiconducting tubes measured), we measure a metallic SWCNT impurity concentration of less than one part per 5519. The decrease of  $G_{on}/G_{off}$ with decreasing  $L_{ch}$  can potentially be explained by irregularities in the packing arrangements within the FET channels. It is clear from the AFM image in Figure S3c that some tubes cross and overlap, which

#### **METHODS**

Preparation of Arc Discharge@PFO-BPy Solutions. Large-diameter, semiconducting enriched SWCNTs are extracted from arc discharge carbon nanotube powder (Nanolab Inc., Waltham, MA, USA). A 1:1 weight ratio of 2 mg/mL of arc discharge soot and PFO-BPy (American Dye Source, Quebec, Canada, 48 K MW) is dispersed in 50 mL of toluene using a horn tip sonicator (Fisher Scientific, Sonic Dismembrator 500) at 64 W power. The sonication time of the initial dispersion is 30 min for SWCNTs prepared in the initial screening and in the surface treatment screening. Initial sonication time is decreased to 5 min after the surface treatment screening. Following the initial dispersion, the SWCNT solution is centrifuged (Thermo Scientific, Sorvall WX, swing bucket rotor, TH-641) at 300000g for 10 min to remove undispersed materials. The upper 90% of the supernatant is collected and centrifuged for an additional 1 h at 300000g. The upper 90% of the supernatant is collected, a 1 mL sample is collected for absorption analysis (see Supporting Information), and the rest is distilled to remove the toluene solvent. The gel-like PFO-BPy SWCNT mixture remaining after distillation is dispersed in tetrahydrofuran (THF). The solution is then centrifuged and dispersed with bath sonication four times in THF to rinse off as much excess PFO-BPy as possible. The final solution is prepared for floating evaporative self-assembly film deposition by horn-tip sonication of the rinsed SWCNT pellet in chloroform for a total of 1 min. The solution is diluted to a final concentration of 10  $\mu$ g/mL prior to floating evaporative self-assembly film deposition and 0.5  $\mu$ g/mL to prepare spincast films.

indicates that there are regions along the length of the tubes that are not in intimate contact with the SiO<sub>2</sub> dielectric. When  $L_{ch}$  is short, some SWCNTs could potentially span the FET channel without ever making contact with the underlying gate dielectric. These noncontacting SWCNTs will be more poorly capacitively coupled to the gate, possibly preventing their complete turn-off. Implementation of a top gate dielectric will be the focus of future work, as it may lead to more uniform gating of the noncontacting SWCNTs.

## CONCLUSIONS

We achieve  $1400 \times$  greater  $G_{on}/G_{off}$  than the previous state of the art, at a comparable  $G_{on}$  per width of  $\sim$ 250  $\mu$ S/ $\mu$ m. Likewise, we achieve 30 $-100 \times$  greater  $G_{\rm on}$  per width than the previous state of the art, at a comparable  $G_{on}/G_{off}$  of  $10^5 - 10^7$ . The excellent performance of the SWCNT FETs varying from L<sub>ch</sub> much shorter to much longer than individual SWCNTs is attributed to the high semiconducting purity, degree of alignment, and packing density of the SWCNTs in the channel. The  $G_{\rm on}$  per tube reaches 5.7  $\pm$  1.4  $\mu$ S and is limited by 2 $R_{\rm c}$  on the order of 100 k $\Omega$ . Mobility is 179  $\pm$  10 cm<sup>2</sup>/V/s at L<sub>ch</sub> of 3  $\mu$ m. These results show that substantially higher  $G_{on}$ per tube and per width should be possible by engineering the contacts and reducing the  $2R_c$  and its variability. These gains highlight the promise of using ultra-highpurity solution-processed semiconducting SWCNTs with controlled alignment for next-generation semiconductor logic, high-frequency linear amplifiers, sensors, and flexible and stretchable electronics.

**Preparation of Aligned SWCNT Films.** During FESA, a receiving substrate is withdrawn from a water trough with control over position and velocity. A thin layer of "ink" (*i.e.*, PFO-BPy-wrapped semiconducting nanotubes in water-immiscible chloroform) is "floated" on the water surface. Here, we deliver ink to the trough surface in discrete "doses" (~2  $\mu$ L droplets). Each droplet spreads until it reaches the substrate, after which a well-defined band of aligned nanotubes is deposited. The band extends across the entire substrate and grows in width as the substrate is withdrawn, until the ink layer is consumed due to evaporation.

SWCNT Surface Treatment Procedure. After depositing the aligned nanotube arrays and defining the channel region with electronbeam lithography (see below), the substrates are rinsed in an acetone bath at 120 °C for 5 min followed immediately by a 120 °C toluene rinse for 5 min and finally a 30 s rinse in isopropyl alcohol. Next the films are annealed in a tube furnace with a 99.999% pure 95% Ar:5% H<sub>2</sub> atmosphere at a temperature of 300 °C for 30 min.

**SWCNT FET Fabrication.** Prior to surface treatment electronbeam lithography is used to define a stripe width of ~4  $\mu$ m, followed by an oxygen plasma etch that removes SWCNTs and material surrounding the FET channel. A second electron-beam step is used to define the source–drain electrodes, which are arranged side-by-side in an array, with different  $L_{chr}$  along the same SWCNT stripe. Thermal deposition of palladium (40 nm) is used to create top contacts to the SWCNTs. Prior to measurement the SWCNT FETs are annealed at 200 °C in a tube furnace with an Ar (99.999%) atmosphere for 1 h.

VOL.8 • NO.11 • 11614-11621 • 2014 A

**Imaging.** SEM images are collected with an LEO-1530 fieldemission scanning electron microscope. Surface morphology and length distributions of the SWCNTs are imaged using a Nanoscope III Multimode atomic force microscope (Digital Instruments).

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. This work was supported by the National Science Foundation Grant No. CMMI-1129802 (G.J.B., M.S.A.). Partial support is also acknowledged from the University of Wisconsin—Madison Center of Excellence for Materials Research and Innovation NSF Grant No. DMR-1121288 (M.-Y.W., Y.J., P.G.) and the U.S. Army Research Office, W911NF-12-1-0025 (M.J.S.). Partial support is also acknowledged from the National Science Foundation Graduate Research Fellowship Program under Grant No. DGE-1256259 (G.J.B.).

Supporting Information Available: Details on AFM length distribution and statistical analysis. Representative device SEM and AFM images. Optimization of surface treatment, sonication time, and gate oxide thickness. Transmission line measurement (TLM) and field-effect mobility calculation using TLM results. Finite-element modeling of channel—gate capacitance for various SWCNT packing arrangements. This material is available free of charge via the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- Durkop, T.; Getty, S. A.; Cobas, E.; Fuhrer, M. S. Extraordinary Mobility in Semiconducting Carbon Nanotubes. *Nano Lett.* 2004, 4, 35–39.

- Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. Ballistic Carbon Nanotube Field-Effect Transistors. *Nature* 2003, 424, 654–657.

- Burke, P. J. Ac Performance of Nanoelectronics: Towards a Ballistic Thz Nanotube Transistor. *Solid-State Electron*. 2004, 48, 1981–1986.

- Franklin, A. D.; Luisier, M.; Han, S. J.; Tulevski, G.; Breslin, C. M.; Gignac, L.; Lundstrom, M. S.; Haensch, W. Sub-10 nm Carbon Nanotube Transistor. *Nano Lett.* **2012**, *12*, 758– 762.

- Jie, Z.; Lin, A.; Patil, N.; Hai, W.; Lan, W.; Wong, H. S. P.; Mitra, S. Carbon Nanotube Robust Digital VLSI. *IEEE Trans. CAD* 2012, *31*, 453–471.

- Guo, J.; Hasan, S.; Javey, A.; Bosman, G.; Lundstrom, M. Assessment of High-Frequency Performance Potential of Carbon Nanotube Transistors. *IEEE Trans. Nanotechnol.* 2005, 4, 715–721.

- Tulevski, G. S.; Franklin, A. D.; Frank, D.; Lobez, J. M.; Cao, Q.; Park, H.; Afzali, A.; Han, S. J.; Hannon, J. B.; Haensch, W. Toward High-Performance Digital Logic Technology with Carbon Nanotubes. ACS Nano 2014, 8, 8730–8745.

- Jin, S. H.; Dunham, S. N.; Song, J.; Xie, X.; Kim, J.-H.; Lu, C.; Islam, A.; Du, F.; Kim, J.; Felts, J.; et al. Using Nanoscale Thermocapillary Flows to Create Arrays of Purely Semiconducting Single-Walled Carbon Nanotubes. *Nat. Nanotechnol.* 2013, 8, 347–355.

- Collins, P. C.; Arnold, M. S.; Avouris, P. Engineering Carbon Nanotubes and Nanotube Circuits Using Electrical Breakdown. *Science* 2001, 292, 706–709.

- Kocabas, C.; Shim, M.; Rogers, J. A. Spatially Selective Guided Growth of High-Coverage Arrays and Random Networks of Single-Walled Carbon Nanotubes and Their Integration into Electronic Devices. J. Am. Chem. Soc. 2006, 128, 4540–4541.

- Ryu, K.; Badmaev, A.; Wang, C.; Lin, A.; Patil, N.; Gomez, L.; Kumar, A.; Mitra, S.; Wong, H. S. P.; Zhou, C. W. CMOS-Analogous Wafer-Scale Nanotube-on-Insulator Approach for Submicrometer Devices and Integrated Circuits Using Aligned Nanotubes. *Nano Lett.* **2009**, *9*, 189–197.

- Hong, S. W.; Banks, T.; Rogers, J. A. Improved Density in Aligned Arrays of Single-Walled Carbon Nanotubes by Sequential Chemical Vapor Deposition on Quartz. *Adv. Mater.* 2010, *22*, 1826–1830.

- Shulaker, M. M.; Wei, H.; Patil, N.; Provine, J.; Chen, H. Y.; Wong, H. S. P.; Mitra, S. Linear Increases in Carbon Nanotube Density through Multiple Transfer Technique. *Nano Lett.* **2011**, *11*, 1881–1886.

- Shulaker, M. M.; Hills, G.; Patil, N.; Wei, H.; Chen, H. Y.; Wong, H. S.; Mitra, S. Carbon Nanotube Computer. *Nature* 2013, 501, 526–530.

- Komatsu, N.; Wang, F. A Comprehensive Review on Separation Methods and Techniques for Single-Walled Carbon Nanotubes. *Materials* **2010**, *3*, 3818–3844.

- Liu, J.; Hersam, M. C. Recent Developments in Carbon Nanotube Sorting and Selective Growth. *MRS Bull.* 2010, 35, 315–321.

- Sun, D. M.; Liu, C.; Ren, W. C.; Cheng, H. M. A Review of Carbon Nanotube- and Graphene-Based Flexible Thin-Film Transistors. *Small* **2013**, *9*, 1188–1205.

- Nish, A.; Hwang, J. Y.; Doig, J.; Nicholas, R. J. Highly Selective Dispersion of Single-Walled Carbon Nanotubes Using Aromatic Polymers. *Nat. Nanotechnol.* 2007, 2, 640– 646.

- Derenskyi, V.; Gomulya, W.; Rios, J. M.; Fritsch, M.; Frohlich, N.; Jung, S.; Allard, S.; Bisri, S. Z.; Gordiichuk, P.; Herrmann, A.; *et al.* Carbon Nanotube Network Ambipolar Field-Effect Transistors with 10 on/Off Ratio. *Adv. Mater.* **2014**, *26*, 5969–5975.

- Shastry, T. A.; Seo, J. W.; Lopez, J. J.; Arnold, H. N.; Kelter, J. Z.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Large-Area, Electronically Monodisperse, Aligned Single-Walled Carbon Nanotube Thin Films Fabricated by Evaporation-Driven Self-Assembly. Small 2013, 9, 45–51.

- Druzhinina, T.; Hoeppener, S.; Schubert, U. S. Strategies for Post-Synthesis Alignment and Immobilization of Carbon Nanotubes. *Adv. Mater.* 2011, *23*, 953–970.

- 22. Yu, G.; Cao, A.; Lieber, C. M. Large-Area Blown Bubble Films of Aligned Nanowires and Carbon Nanotubes. *Nat. Nanotechnol.* **2007**, *2*, 372–377.

- LeMieux, M. C.; Roberts, M.; Barman, S.; Jin, Y. W.; Kim, J. M.; Bao, Z. Self-Sorted, Aligned Nanotube Networks for Thin-Film Transistors. *Science* **2008**, *321*, 101–104.

- Cao, Q.; Han, S. J.; Tulevski, G. S.; Zhu, Y.; Lu, D. D.; Haensch, W. Arrays of Single-Walled Carbon Nanotubes with Full Surface Coverage for High-Performance Electronics. *Nat. Nanotechnol.* **2013**, *8*, 180–186.

- Jia, L.; Zhang, Y.; Li, J.; You, C.; Xie, E. Aligned Single-Walled Carbon Nanotubes by Langmuir–Blodgett Technique. *J. Appl. Phys.* 2008, 104, 074318.

- Liu, H.; Takagi, D.; Chiashi, S.; Homma, Y. Transfer and Alignment of Random Single-Walled Carbon Nanotube Films by Contact Printing. ACS Nano 2010, 4, 933–938.

- Shekhar, S.; Stokes, P.; Khondaker, S. I. Ultrahigh Density Alignment of Carbon Nanotube Arrays by Dielectrophoresis. ACS Nano 2011, 5, 1739–1746.

- Liyanage, L. S.; Lee, H.; Patil, N.; Park, S.; Mitra, S.; Bao, Z. N.; Wong, H. S. P. Wafer-Scale Fabrication and Characterization of Thin-Film Transistors with Polythiophene-Sorted Semiconducting Carbon Nanotube Networks. ACS Nano 2012, 6, 451–458.

- Park, S.; Lee, H. W.; Wang, H. L.; Selvarasah, S.; Dokmeci, M. R.; Park, Y. J.; Cha, S. N.; Kim, J. M.; Bao, Z. A. Highly Effective Separation of Semiconducting Carbon Nanotubes Verified via Short-Channel Devices Fabricated Using Dip-Pen Nanolithography. ACS Nano 2012, 6, 2487–2496.

- Stokes, P.; Khondaker, S. I. High Quality Solution Processed Carbon Nanotube Transistors Assembled by Dielectrophoresis. *Appl. Phys. Lett.* 2010, *96*, 3.

- Lin, Y. M.; Appenzeller, J.; Chen, Z. H.; Chen, Z. G.; Cheng, H. M.; Avouris, P. High-Performance Dual-Gate Carbon Nanotube FETs with 40-nm Gate Length. *IEEE Electron Device Lett.* 2005, 26, 823–825.

- Xu, W.; Zhao, J.; Qian, L.; Han, X.; Wu, L.; Wu, W.; Song, M.; Zhou, L.; Su, W.; Wang, C.; *et al.* Sorting of Large-Diameter Semiconducting Carbon Nanotube and Printed Flexible Driving Circuit for Organic Light Emitting Diode (OLED). *Nanoscale* **2014**, *6*, 1589–1595.

- Park, H.; Afzali, A.; Han, S. J.; Tulevski, G. S.; Franklin, A. D.; Tersoff, J.; Hannon, J. B.; Haensch, W. High-Density Integration of Carbon Nanotubes via Chemical Self-Assembly. *Nat. Nanotechnol.* 2012, 7, 787–791.

- Joo, Y.; Brady, G. J.; Arnold, M. S.; Gopalan, P. Dose-Controlled, Floating Evaporative Self-Assembly and Alignment of Semiconducting Carbon Nanotubes from Organic Solvents. *Langmuir* 2014, *30*, 3460–3466.

- Brady, G. J.; Joo, Y.; Roy, S. S.; Gopalan, P.; Arnold, M. S. High Performance Transistors Via Aligned Polyfluorene-Sorted Carbon Nanotubes. *Appl. Phys. Lett.* **2014**, *104*, 5.

- Mistry, K. S.; Larsen, B. A.; Blackburn, J. L. High-Yield Dispersions of Large-Diameter Semiconducting Single-Walled Carbon Nanotubes with Tunable Narrow Chirality Distributions. ACS Nano 2013, 7, 2231–2239.

- Bindl, D. J.; Wu, M. Y.; Prehn, F. C.; Arnold, M. S. Efficiently Harvesting Excitons from Electronic Type-Controlled Semiconducting Carbon Nanotube Films. *Nano Lett.* 2011, *11*, 455–460.

- Engel, M.; Small, J. P.; Steiner, M.; Freitag, M.; Green, A. A.; Hersam, M. S.; Avouris, P. Thin Film Nanotube Transistors Based on Self-Assembled, Aligned, Semiconducting Carbon Nanotube Arrays. ACS Nano 2008, 2, 2445–2452.

- Kang, S. J.; Kocabas, C.; Ozel, T.; Shim, M.; Pimparkar, N.; Alam, M. A.; Rotkin, S. V.; Rogers, J. A. High-Performance Electronics Using Dense, Perfectly Aligned Arrays of Single-Walled Carbon Nanotubes. *Nat. Nanotechnol.* 2007, 2, 230–236.

- Kim, B.; Jang, S.; Prabhumirashi, P. L.; Geier, M. L.; Hersam, M. C.; Dodabalapur, A. Low Voltage, High Performance Inkjet Printed Carbon Nanotube Transistors with Solution Processed ZrO<sub>2</sub> Gate Insulator. *Appl. Phys. Lett.* **2013**, *103*, 082119.

- King, B.; Panchapakesan, B. Vacuum Filtration Based Formation of Liquid Crystal Films of Semiconducting Carbon Nanotubes and High Performance Transistor Devices. *Nanotechnology* 2014, 25, 14.

- 42. Miyata, Y.; Shiozawa, K.; Asada, Y.; Ohno, Y.; Kitaura, R.; Mizutani, T.; Shinohara, H. Length-Sorted Semiconducting Carbon Nanotubes for High-Mobility Thin Film Transistors. *Nano Res.* **2011**, *4*, 963–970.

- Sangwan, V. K.; Ortiz, R. P.; Alaboson, J. M. P.; Emery, J. D.; Bedzyk, M. J.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Fundamental Performance Limits of Carbon Nanotube Thin-Film Transistors Achieved Using Hybrid Molecular Dielectrics. ACS Nano 2012, 6, 7480–7488.

- Sun, D. M.; Timmermans, M. Y.; Tian, Y.; Nasibulin, A. G.; Kauppinen, E. I.; Kishimoto, S.; Mizutani, T.; Ohno, Y. Flexible High-Performance Carbon Nanotube Integrated Circuits. *Nat. Nanotechnol.* **2011**, *6*, 156–161.

- Wu, J.; Jiao, L.; Antaris, A.; Choi, C. L.; Xie, L.; Wu, Y.; Diao, S.; Chen, C.; Chen, Y.; Dai, H. Self-Assembly of Semiconducting Single-Walled Carbon Nanotubes into Dense, Aligned Rafts. *Small* **2013**, *9*, 4142–4148.

- Wu, J.; Antaris, A.; Gong, M.; Dai, H. Top-Down Patterning and Self-Assembly for Regular Arrays of Semiconducting Single-Walled Carbon Nanotubes. *Adv. Mater.* 2014, *26*, 6151–6156.

- Kim, W.; Jarvey, A.; Vermesh, O.; Wang, Q.; Li, Y.; Dai, H. Hysteresis Caused by Water Molecules in Carbon Nanotube Field-Effect Transistors. *Nano Lett.* **2003**, *3*, 193–198.

- Wang, C.; Qian, L.; Xu, W.; Nie, S.; Gu, W.; Zhang, J.; Zhao, J.; Lin, J.; Chen, Z.; Cui, Z. High Performance Thin Film Transistors Based on Regioregular Poly(3dodecylthiophene)-Sorted Large Diameter Semiconducting Single-Walled Carbon Nanotubes. *Nanoscale* **2013**, *5*, 4156–4161.

- Ortiz-Conde, A.; Sanchez, F. J. G.; Liou, J. J.; Cerdeira, A.; Estrada, M.; Yue, Y. A Review of Recent Mosfet Threshold Voltage Extraction Methods. *Microelectron. Reliab.* 2002, 42, 583–596.

- Franklin, A. D. F.; Damon, B.; Haensch, W. Defining and Overcoming the Contact Resistance Challenge in Scaled Carbon Nanotube Transistors. ACS Nano 2014, 8, 7333– 7339.

- Joo, M.-K. K.; Un J.; Jeon, D.-Y.; Park, S. J.; Mouis, M.; Kim, G.-T.; Ghibaudo, G. Static and Low Frequency Noise Characterization of Densley Packed Cnt-Tfts. *Proceedings* of the European Solid-State Device Research Conference (ESSDERC), 2012; 2012; pp 129–132.

- Cao, Q.; Han, S. J.; Tulevski, G. S.; Franklin, A. D.; Haensch, W. Evaluation of Field-Effect Mobility and Contact Resistance of Transistors That Use Solution-Processed Single-Walled Carbon Nanotubes. ACS Nano 2012, 6, 6471–6477.

- Wang, C. A.; Ryu, K. M.; De Arco, L. G.; Badmaev, A.; Zhang, J. L.; Lin, X.; Che, Y. C.; Zhou, C. W. Synthesis and Device Applications of High-Density Aligned Carbon Nanotubes Using Low-Pressure Chemical Vapor Deposition and Stacked Multiple Transfer. *Nano Res.* **2010**, *3*, 831–842.

- Ho, X. N.; Ye, L. N.; Rotkin, S. V.; Cao, Q.; Unarunotai, S.; Salamat, S.; Alam, M. A.; Rogers, J. A. Scaling Properties in Transistors That Use Aligned Arrays of Single-Walled Carbon Nanotubes. *Nano Lett.* **2010**, *10*, 499–503.

- Wager, J. F.; Yeh, B.; Hoffman, R. L.; Keszler, D. A. An Amorphous Oxide Semiconductor Thin-Film Transistor Route to Oxide Electronics. *Curr. Opin. Solid State Mater. Sci.* 2014, *18*, 53–61.